Building software consistently across environments requires more than manual compilation commands. A well-crafted Makefile transforms repetitive tasks into reliable, repeatable processes. While basic Makefile syntax is accessible, mastering its full potential—variables, dependencies, pattern rules, and automation logic—elevates development efficiency. This guide dives deep into intermediate and advanced techniques that empower developers to create scalable, maintainable build systems using GNU Make.

Understanding the Core Mechanics of Make

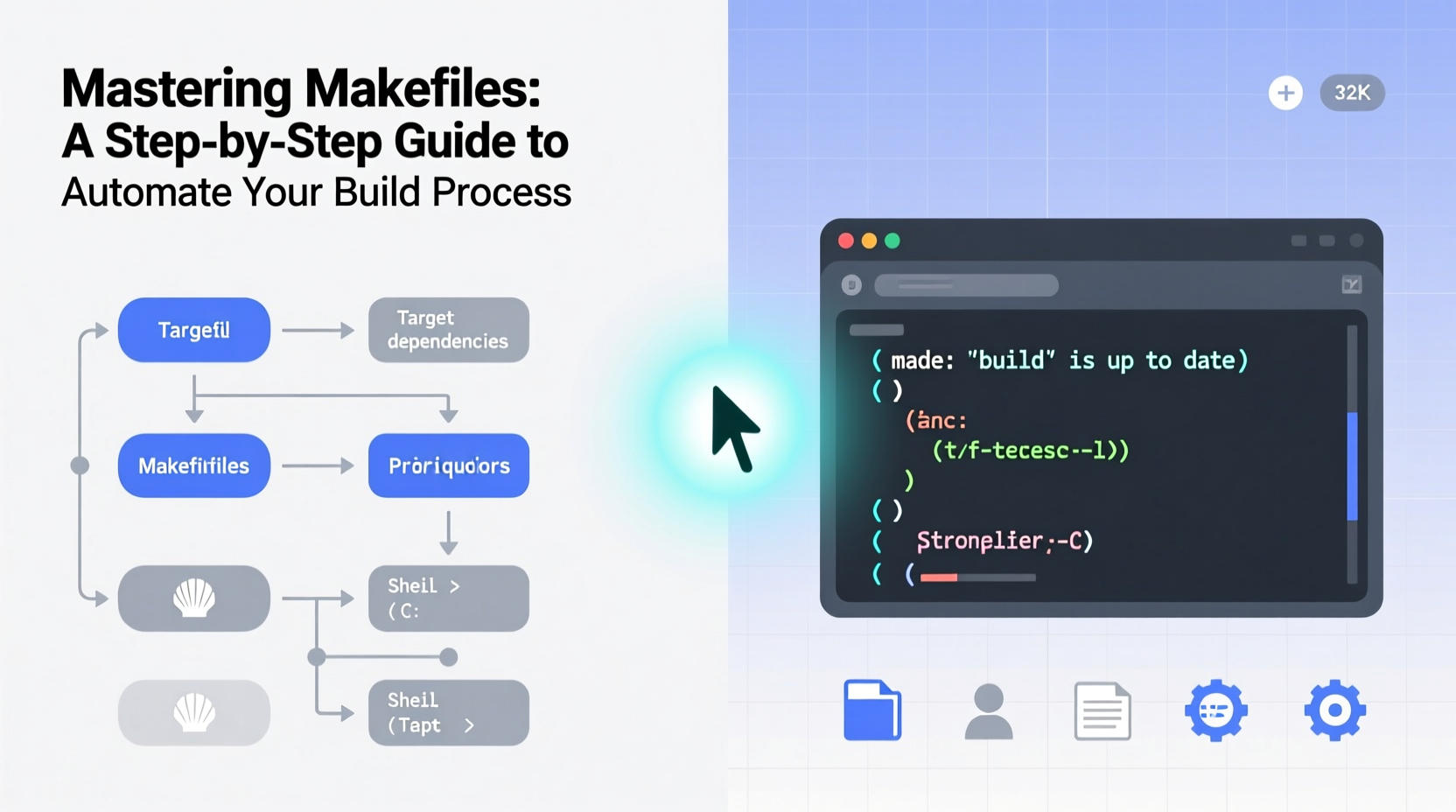

At its foundation, Make analyzes file dependencies and executes commands only when necessary. Each rule in a Makefile consists of a target, prerequisites (dependencies), and recipes (commands). The engine checks timestamps: if any prerequisite is newer than the target, the recipe runs.

This dependency-driven model prevents redundant work. For example, recompiling every source file after a single change wastes time. Make avoids this by tracking which object files need updating based on changes in corresponding C or C++ sources.

“Make isn’t just about compiling code—it’s about modeling relationships between artifacts.” — Karl Beldan, Build Systems Engineer at Mozilla

The power lies in expressing these relationships clearly. Misconfigured dependencies lead to incomplete builds or unnecessary rebuilds, both undermining reliability.

Advanced Pattern Rules and Wildcards

Writing individual rules for each source file becomes impractical in large projects. Pattern rules solve this by applying logic across multiple files using special characters like %.

For instance, converting all .c files to .o objects:

%.o: %.c

$(CC) -c $< -o $@

Here, % matches any non-empty substring, so main.c maps to main.o. Variables like $< (first prerequisite) and $@ (target) simplify command writing.

Combine this with automatic source discovery:

SOURCES := $(wildcard *.c) OBJECTS := $(SOURCES:.c=.o)

This dynamically generates a list of object files from available C sources, eliminating hardcoded entries.

$(wildcard) and substitution references to keep your Makefile adaptive as your project grows.

Managing Variables and Configuration

Effective Makefiles separate configuration from logic. Define toolchain settings, flags, and paths at the top for easy adjustment.

| Variable | Purpose | Example Value |

|---|---|---|

| CC | C compiler | gcc |

| CFLAGS | Compilation flags | -Wall -O2 |

| LDFLAGS | Linker flags | -lm |

| BIN | Output binary name | app |

Use conditional assignment operators wisely:

:=– Immediate evaluation=– Deferred (recursive) expansion?=– Set only if not already defined

This allows environment overrides without breaking defaults:

CFLAGS ?= -O2 -g

Now users can run CFLAGS=\"-O3\" make to customize optimization without editing the file.

Step-by-Step: Building a Modular Project Structure

Consider a project with source files in src/, headers in include/, and output binaries in bin/. Here's how to structure the Makefile accordingly.

- Define directories:

SRC_DIR = src

INC_DIR = include

BIN_DIR = bin - Discover source files:

SOURCES := $(wildcard $(SRC_DIR)/*.c)

OBJECTS := $(SOURCES:$(SRC_DIR)/%.c=$(BIN_DIR)/%.o) - Create output directory automatically:

$(BIN_DIR)/%.o: $(SRC_DIR)/%.c

@mkdir -p $(dir $@)

$(CC) $(CFLAGS) -I$(INC_DIR) -c $< -o $@ - Link final binary:

$(BIN_DIR)/app: $(OBJECTS)

$(CC) $(LDFLAGS) $^ -o $@ - Add clean and all targets:

all: $(BIN_DIR)/app

clean:

rm -rf $(BIN_DIR)

This setup ensures proper separation of concerns, automatic directory creation, and clean rebuilds.

Avoiding Common Pitfalls

Even experienced developers trip over subtle Make behaviors. Recognizing these issues early saves debugging hours.

- Missing dependencies: If a header file changes but isn't listed as a prerequisite, dependent object files won't rebuild.

- Tab vs. spaces: Recipes must begin with a literal tab character. Using spaces causes a cryptic error.

- Phony targets confusion: Targets like

cleanaren’t files. Mark them with.PHONY: cleanto prevent conflicts. - Overuse of recursion: Deeply nested Make calls complicate dependency tracking and slow execution.

.PHONY for non-file targets such as

build,

test, or

install.

Real Example: Automating a Multi-Language Build

A team maintains a hybrid application combining C modules and Python scripts. They use Make to compile performance-critical components while packaging Python code into an executable bundle via PyInstaller.

Their Makefile defines:

.PHONY: all c_build python_bundle clean

all: c_build python_bundle

c_build:

$(MAKE) -C src/fast_module

python_bundle:

pyinstaller --onefile main.py

clean:

$(MAKE) -C src/fast_module clean

rm -rf dist/ build/ *.spec

This orchestrates two independent build systems under one interface. Developers run make once to produce a complete distributable, regardless of language boundaries.

The result? Faster CI pipelines, consistent local builds, and reduced onboarding friction for new contributors.

Expert Checklist for Production-Ready Makefiles

Before deploying a Makefile in a team or CI environment, verify these points:

- ✅ All source-to-object dependencies are correctly declared

- ✅ Header files are included in prerequisites where needed

- ✅ Output directories are created before use

- ✅ Phony targets are explicitly declared

- ✅ Variables are documented or self-explanatory

- ✅ Clean target removes all generated files

- ✅ Works from any directory (uses relative paths)

- ✅ Supports override via environment (e.g.,

CC=clang make)

This checklist ensures robustness across different machines and usage scenarios.

Frequently Asked Questions

Can Make detect changes in header files automatically?

No—not by default. You must explicitly list header dependencies or generate them using compiler features. GCC supports this with -MM to output dependency graphs. Integrate it via:

$(shell gcc -MM *.c)

Or include dynamic deps in the Makefile using include and a generated .d file per source.

Is Make still relevant with modern tools like CMake or Ninja?

Absolutely. While higher-level tools exist, Make remains foundational. Many build generators output Makefiles. Understanding Make gives insight into what those tools produce and enables quick scripting without external dependencies.

How do I debug a failing Makefile?

Use built-in flags:

make -n: Show commands without running them (dry run)make -d: Print detailed dependency analysis and decisionsmake --warn-undefined-variables: Catch typos in variable names

Conclusion: Turn Build Chaos into Predictable Automation

Mastering Makefiles is not merely about learning syntax—it’s about adopting a mindset of reproducibility and precision. Every automated build reduces human error, accelerates development cycles, and strengthens collaboration. Whether you're managing a small utility or integrating complex multi-component systems, a well-designed Makefile serves as the backbone of reliable software delivery.

浙公网安备

33010002000092号

浙公网安备

33010002000092号 浙B2-20120091-4

浙B2-20120091-4

Comments

No comments yet. Why don't you start the discussion?